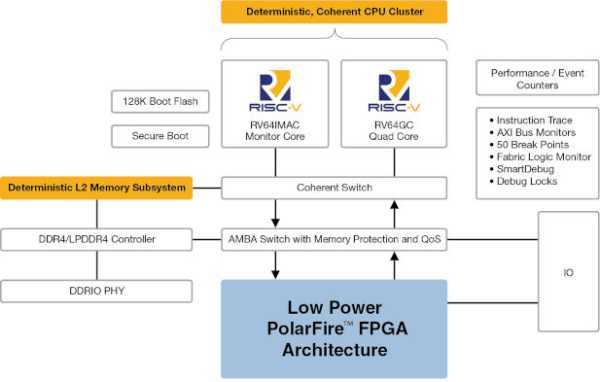

Називається &# 8216;PolarFire SoC’, архітектура забезпечує можливість детермінованої асиметричної багатопроцесорної обробки в реальному часі на платформах Linux у багатоядерному узгодженому кластері ЦП, за словами фірми, яка працювала зі спеціалістом із Risc-V SiFive. для створення пристроїв.

Операції в режимі реального часу включено для критично важливих для безпеки, системного керування та надійних середовищ виконання.

Це досягається шляхом вимкнення прогностиків розгалужень ЦП, перетворення рівня 1 кешувати до тісно інтегрованої пам’яті, гарантуючи, що всі ядра узгоджені з підсистемою пам’яті та спільно використовують узгоджену пам’ять для передачі повідомлень.

Чотири ядра виконують набір інструкцій RV64GC. Для їх моніторингу існує п’ятий 64-розрядний Risc-V, який цього разу виконує набір інструкцій RV64IMAC. Усі п’ять можуть працювати узгоджено.

Від існуючих PolarFire FPGA версії Risc-V успадкували функції безпеки, зокрема: стійке до DPA програмування бітового потоку, захист від несанкціонованого втручання, криптографічну прив’язану гарантію ланцюга поставок, фізичну несправність – функція клонування, справжній генератор випадкових чисел і стійкий до побічних каналів крипто-співпроцесор.

Крім того, згідно з Microchip, процесори матимуть безпечне завантаження (128 Кбайт завантажувальної флеш-пам’яті), захист фізичної пам’яті та, на всіх видах пам’яті: однобітне виправлення помилок і двобітне виявлення помилок. Фірма також заявляє про захист від Spectre та Meltdown.

До того як чіпи стануть доступними, можна використовувати фреймворк Renode з відкритим вихідним кодом від Antmicro, а Microchip створила ‘HiFive Unleashed Expansion Дошка’ працювати разом із HiFive‘Unleashed Development Board’ – Microchip назвала обидві плати разом: MPFS-DEV-KIT.

Для існуючих PolarFire FPGA Microchip має ‘Mi-V’ 32-розрядні програмні ядра Risc-V, які виконують набір інструкцій RV32I (цілочисельний), деякі з ‘M’ (помножити/поділити), ‘A’ (атомна інструкція) або ‘F’ (з плаваючою точкою одинарної точності).

Microchip, представлений на ‘Getting Started with RISC-V’ минулого тижня в Лондоні.

Источник: electronicsweekly.com